Contact person: Dr. Marina Zapater ([email protected]), Prof. David Atienza ([email protected])

Partners

Computer Architecture and Automation Department (DACYA), UCM, Spain;

Presentation

High-Performance Computing (HPC) as we know it today is experimenting unprecedented challenges, mainly due to the advent of new HPC Quality-of-Service (QoS) constrained applications, which exhibit the high computational demands of traditional HPC, together with real-time requirements. Existing MPSoCs and servers have been optimized over many generations eliminating low-hanging fruits for further improvement. Thus, to achieve the required efficiency required by next-generation workloads, there is a need to take disruptive approaches towards the development of new processor architectures.

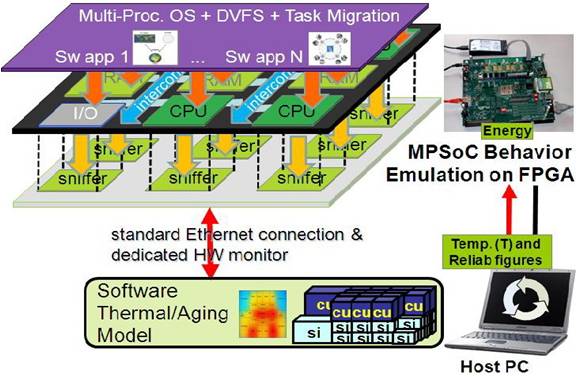

To enable architectural exploration, the usage of simulators is a must. In order to explore the HW/SW interaction, MPSoC simulators have been developed at the transaction and cycle-accurate levels, using HDL languages and SystemC. Also, several SW tools recently developed can be added to them to evaluate thermal pressure in on-chip components based on run-time power consumption and floorplanning information of MPSoCs. Nevertheless, these complex SW environments are limited in performance and unsuitable for large-scale simulation of many-core servers running real HPC applications. Moreover, higher abstraction levels simulators attain faster simulation speeds, but at the cost of a significant loss of accuracy. Hence, they are not suitable for fine-grained architectural tuning and thermal, power, performance and reliability modeling.

One solution for the speed problems of cycle-accurate simulators is HW emulation. However, it is usually very expensive for embedded design (between $100K and $1M). Moreover, it is not flexible enough for MPSoC architecture exploration since they mainly aim at large MPSoCs prototyping or SW debugging. Typically, the baseline architectures (e.g. processing cores or interconnections) are proprietary, not permitting internal changes. Furthermore, no flexible interconnection interfaces between HW emulation and the existing SW thermal libraries exist today. Thus, thermal and reliability effects can only be verified in the last phases of the design process, when the final components are available, which can produce large overheads in the production process due to cores and overall MPSoC architecture redesigns.

Goal

The purpose of this research line is to develop a HW/SW simulation framework together with an efficient FPGA- and GPU-based emulation platform that enables exploring a large number of design alternatives of MPSoCs at multiple layers, from cycle-accurate architectural simulation to functional MPSoC and server simulation, up to the large-scale simulation of many-core servers in data centers. In this sense, the simulation/emulation infrastructure will allow the exploration of the thermal/power/performance trade-offs of next-generation high-performance computing applications while running on heterogeneous many-core platforms.

This work involves defining flexible HW emulation interfaces for on-chip MPSoC components interacting in real-time with SW thermal, power, performance and reliability models running on a host system with a high-speed network connection.

Developed software tools:

- GPU Accelerated Full System Simulation of Heterogeneous Many-core Platforms (SIMinG)

- The 3D-ICE thermal simulator

Related projects:

- ERC Consolidator project COMPUSAPIEN

Publications:

- S. Raghav, M. Ruggiero, A. Marongiu, C. Pinto and D. Atienza et al. GPU Acceleration for Simulating Massively Parallel Many-Core Platforms, in IEEE Transactions On Parallel And Distributed Systems, vol. 26, num. 5, p. 1336-1349, 2015.

- S. Raghav, A. Marongiu, C. Pinto, M. Ruggiero and D. Atienza et al. SIMinG-1k: A thousand-core simulator running on general-purpose graphical processing units, in Concurrency And Computation – Practice and Experience, vol. 25, num. 10, p. 1443-1461, 2013.