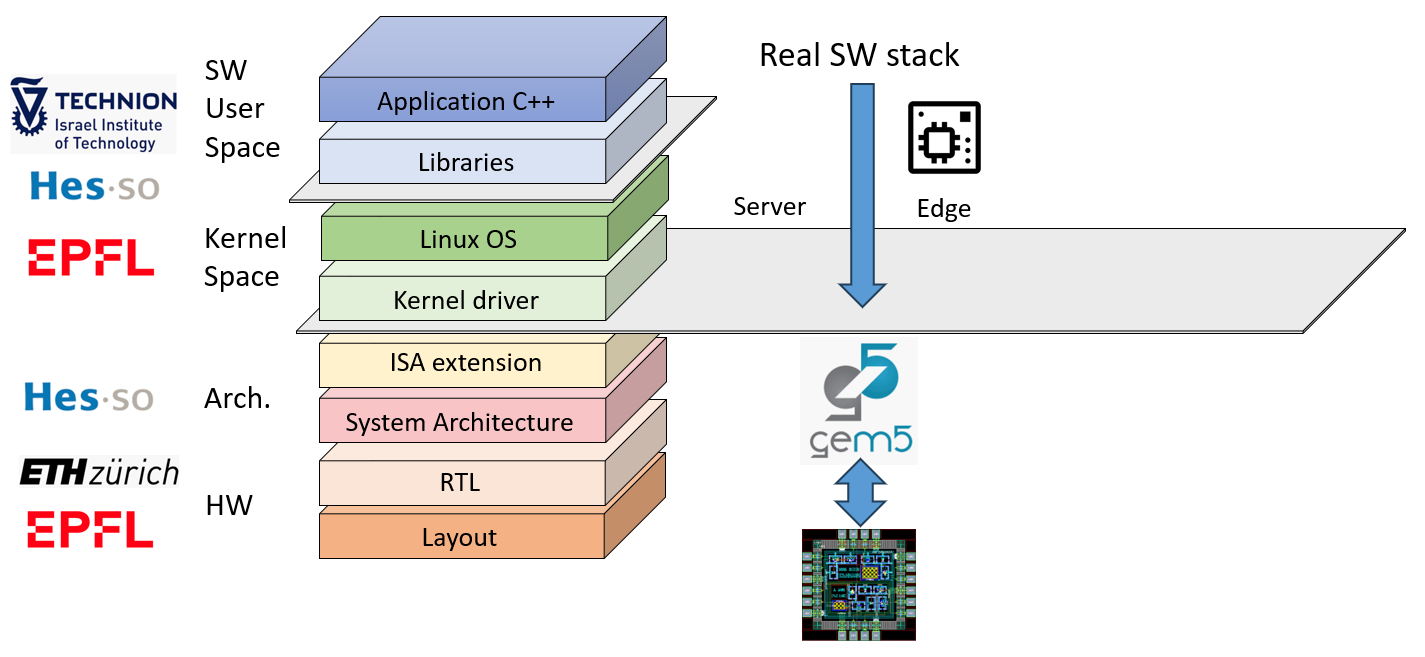

2D/3D heterogeneous chiplet-based systems are a key enabler for moving Artificial Intelligence (AI) from the datacenter to the edge. Novel accelerators and interconnects are key for enhancing efficiency for both edge (energy-optimized) and HPC (performance-optimized) systems. A seamless path from software (SW) to hardware (HW) needs to be enabled to allow block reuse and disaggregation and to assess the overall SW-HW stack in terms of performance, power and thermal constraints.

The CHIMP project puts together the complementary expertise of research labs ranging from HW (technology and architecture) to software (system-level, operating system and applications) to devise a multi-objective full-stack simulation framework, able to provide design guidelines and assess efficiency at all levels of the stack.

The expertise of researchers from the different institutions, which are intertwined at the different levels of the SW/HW stack, make CHIMP a truly collaborative project whose synergies will enable the simulation and assessment of 2D/3D heterogeneous chiplets at all layers of the stack.

Software systems (Daniel Rossier from HES-SO and Yoav Etsion from Technion)

Innovative software stack based on lightweight and monolithic operating systems, which will be enhanced during the project to tackle both edge and cloud systems

Novel software primitives focusing on novel workloads and that rely on microservices, virtualization (including containers), task mapping and distributed execution.

Hardware systems (Marina Zapater from HES-SO and Babak Falsafi from EPFL)

Using the hardware models developed as part of RV2 as building blocs for the simulation of heterogeneous systems. Addressing intelligent disaggregation and reuse via multi-objective (performance/energy/thermal) exploration of the resulting design space.

Thermal exploration of heterogeneous chiplet-based systems under traditional and novel dissipation techniques, including heat spreaders, fans, but also heat pipes, interlayer liquid cooling or two-phase cooling.

Hardware modelling and implementation (David Atienza from EPFL and Onur Mutlu from ETHZ)

Designing novel accelerator models for digital and analog computation, and their integration as part of the 2.5D/3D chiplet

Proposing novel disruptive interconnects (photonics, in-package wireless) as well as novel memory partitioning systems

RV2 – Proposing the implementation of the solution as embedded IPs targetting the Intel 16nm technology

Read more

Related Publications

| A 20-Year Retrospective on Power and Thermal Modeling and Management | ||||

| Atienza, David; Zhu, Kai; Huang, Darong; Costero, Luis | ||||

| 2025-08-07 | IEEE Design & Test |  |  | |

| Cross-layer Exploration of 2.5D Energy-Efficient Heterogeneous Chiplets Integration: From System Simulation to Open Hardware | ||||

| Burdina, Anna; Catel Torres, Gabriel; Schiavone, Davide; Peon-Quiros, Miguel; Ansaloni, Giovanni; Atienza, David; Zapater, Marina | ||||

| 2024-08-05 | Proceedings of the 29th International Symposium on Low Power Electronics and Design, ISLPED 2024 | 29 ACM/IEEE International Symposium on Low Power Electronics and Design |  | |