LTS5 research in ultrasound imaging

Regularization methods in ultrasound imaging

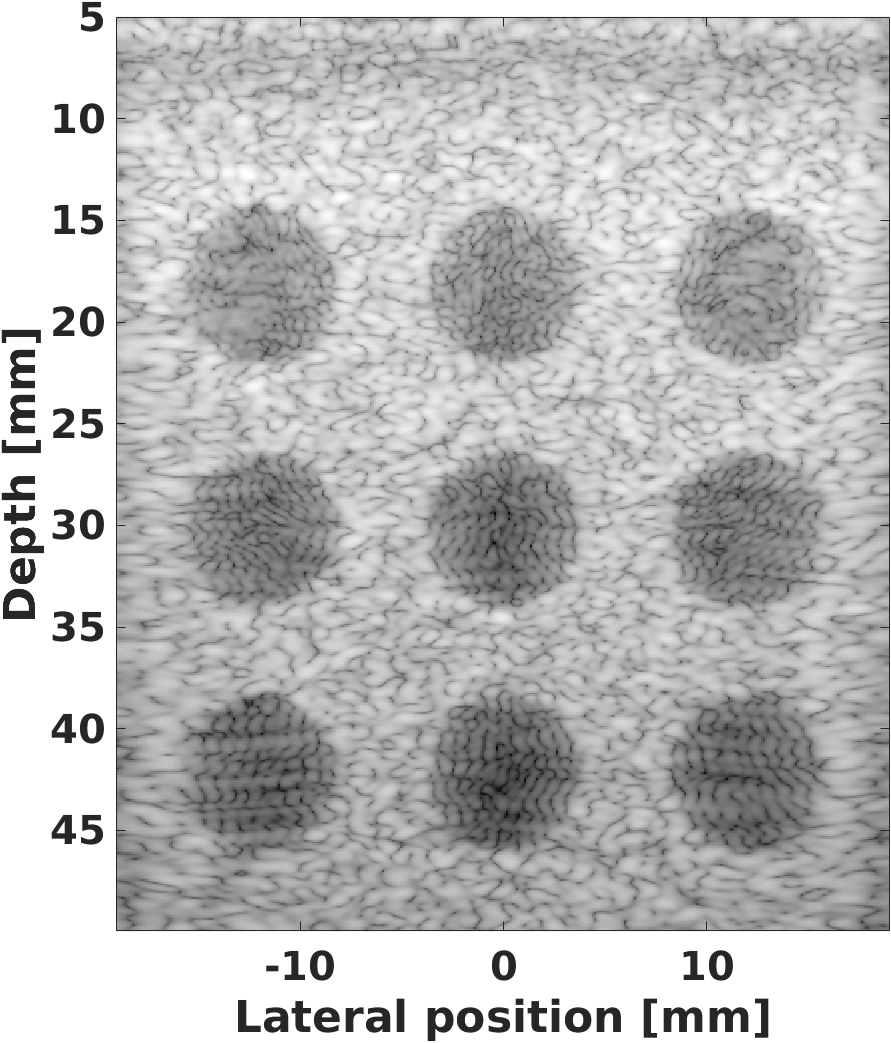

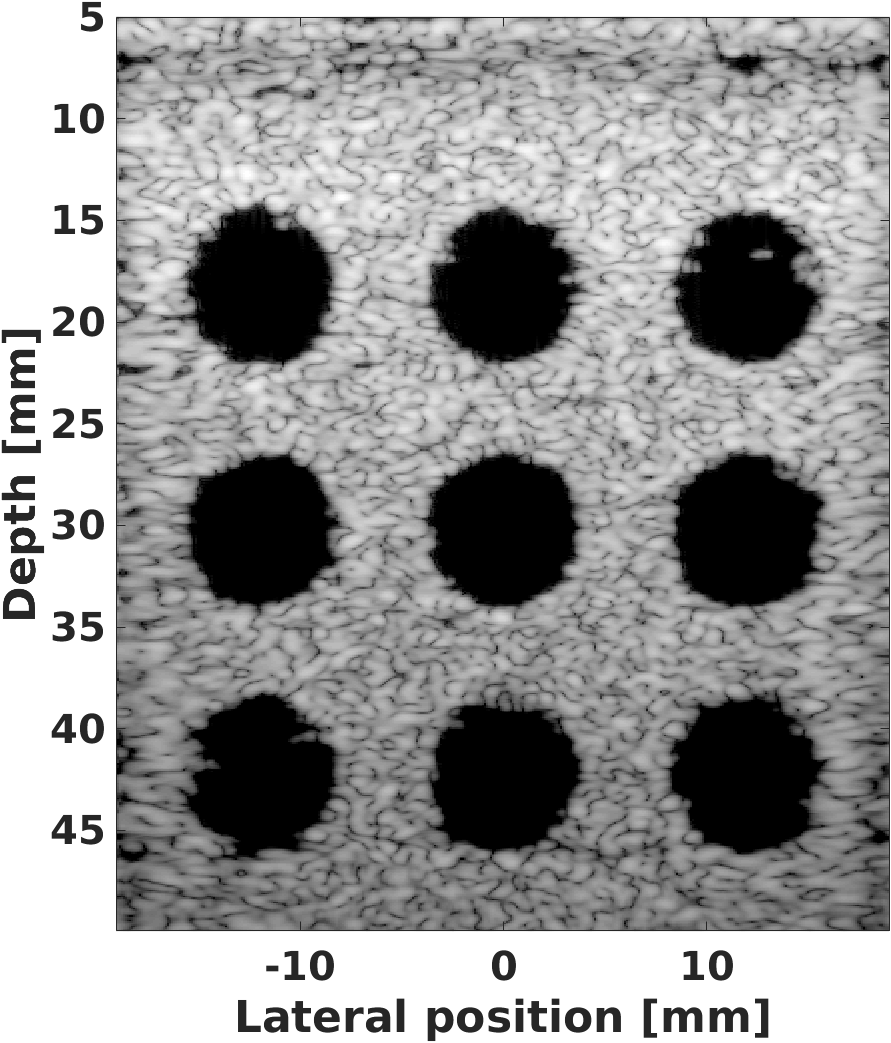

In terms of acoustic wave propagation, ultrasound imaging poses an inverse problem which relates the tissue reflectivity (image under scrutiny) to the backscattered echoes (the measurements). Standard imaging methods are based on a well-known algorithm called Delay-and-sum (DAS). The major advantage of DAS is that it is fast and highly parallelizable. Its main drawback is that it is an inaccurate solution of the inverse problem which leads to low-quality images. One research topic in LTS5 consists in exploring alternatives to DAS mainly based on regularization approaches. The idea is to inject prior knowledge (sparsity of the image in a well-chosen model) about the tissue reflectivity in order to leverage the ill-posedness of the problem. The problem is recast as a convex optimization algorithm and solved using standard algorithms such as ADMM, primal-dual forward backward or FISTA.

Figure: Cyst image reconstructed with the DAS algorithm (left) and with the sparse regularization approach (right).

Compressed sensing and deep learning in ultrasound imaging

Compressed sensing or compressive sensing (CS) is a well-known mathematical framework which ensures perfect recovery of compressible signals from random projections with fewer samples than Nyquist rate. The recovery is achieved by solving a convex optimization problem where the most compressible solution which fits to the measurements is identified. This framework has been substantially studied in the last ten years and has lead to great successes such as: the Rice single pixel camera or the Sparse MRI. At LTS5, we are currently working on applying the CS framework to ultrasound imaging. The first idea is to exploit the intrinsic structure of US data which can be modelled as a stream of pulses, compressible in a redundant dictionary made of shifted replica of the ultrasound pulse. The second idea consists in designing acquisition schemes that are most suited to the CS framework. The last work focuses on designing efficient reconstruction algorithms. To do so, we are intensively working on deep learning algorithms which are becoming extremely popular nowadays due to their ability to perform a various of tasks (object recognition, classification, text generation, image colorization etc.). At LTS5, we are currently focusing on three main deep neural netwrok architectures for ultrasound imaging:

- DNN that maps convex optimization algorithms such as Fast-Iterative thredsholding algorithm (FISTA);

- Fully connected architectures (Stacked denoising autoencoders, Multi-layer perceptron);

- Convolutional neural networks.

Please note that the publication lists from Infoscience integrated into the EPFL website, lab or people pages are frozen following the launch of the new version of platform. The owners of these pages are invited to recreate their publication list from Infoscience. For any assistance, please consult the Infoscience help or contact support.

An Implantable Wireless System for Remote Hemodynamic Monitoring of Heart Failure Patients

Ieee Transactions On Biomedical Circuits And Systems. 2023-08-01. Vol. 17, num. 4, p. 688-700. DOI : 10.1109/TBCAS.2023.3273711.Design Space Exploration for Partitioning Dataflow Program on CPU-GPU Heterogeneous System

Journal Of Signal Processing Systems For Signal Image And Video Technology. 2023-07-31. DOI : 10.1007/s11265-023-01884-6.Toward a common standard for data and specimen provenance in life sciences

Learning Health Systems. 2023-04-18. p. e10365. DOI : 10.1002/lrh2.10365.FM -Directories: Extending the Burrows-Wheeler Transform for String Labeled Vertex Graphs of (Almost) Arbitrary Topology

2023-01-01. Data Compression Conference (DCC), Snowbird, UT, Mar 21-24, 2023. p. 355-355. DOI : 10.1109/DCC55655.2023.00087.Integrated Electronics for Deep Implants to Remotely Monitor Hemodynamics

Lausanne, EPFL, 2023.Compilation and Design Space Exploration of Dataflow Programs for Heterogeneous CPU-GPU Platforms

Lausanne, EPFL, 2023.The impact of NFT profile pictures within social network communities

2022-09-30. GoodIT 2022: ACM International Conference on Information Technology for Social Good, Limassol, Cyprus, September 7 – 9, 2022. p. 283-291. DOI : 10.1145/3524458.3547230.Dynamic SIMD Parallel Execution on GPU from High-Level Dataflow Synthesis

Journal Of Low Power Electronics And Applications. 2022-09-01. Vol. 12, num. 3, p. 40. DOI : 10.3390/jlpea12030040.Performance Estimation of High-Level Dataflow Program on Heterogeneous Platforms by Dynamic Network Execution

Journal Of Low Power Electronics And Applications. 2022-09-01. Vol. 12, num. 3, p. 36. DOI : 10.3390/jlpea12030036.An Energy-Efficient Bridge-to-Digital Converter for Implantable Pressure Monitoring Systems

IEEE Transactions on Biomedical Circuits and Systems. 2022-07-04. Vol. 16, num. 5, p. 732-741. DOI : 10.1109/TBCAS.2022.3187828.SIMD Parallel Execution on GPU from High-Level Dataflow Synthesis

2022-02-04. 14th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), Singapore, December 20-23, 2021. p. 62-68. DOI : 10.1109/MCSoC51149.2021.00017.Performance Estimation of High-Level Dataflow Program on Heterogeneous Platforms

2022-02-04. 14th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), Singapore, December 20-23, 2021. p. 69-76. DOI : 10.1109/MCSoC51149.2021.00018.An Implantable Inductive Sensor for Direct and Continuous Monitoring of the Pulmonary Artery Cross-Sectional Area

2022. 2022 IEEE Biomedical Circuits and Systems Conference (BioCAS), Taipei, Taiwan, October 13-15, 2022. p. 31-35. DOI : 10.1109/BioCAS54905.2022.9948566.A Capacitively-Coupled Chopper Instrumentation Amplifier for Implantable Bridge Sensor Systems

2022-01-01. 20th IEEE Interregional NEWCAS Conference (IEEE NEWCAS), Quebec City, CANADA, Jun 19-22, 2022. p. 208-212. DOI : 10.1109/NEWCAS52662.2022.9842137.MPEG-G Reference-Based Compression of Unaligned Reads Through Ultra-Fast Alignments

2022-01-01. Data Compression Conference (DCC), Snowbird, UT, Mar 22-25, 2022. p. 478-478. DOI : 10.1109/DCC52660.2022.00089.Inter-actions parallel execution on GPU from high-level dataflow synthesis

2022. 2021 55th Asilomar Conference on Signals, Systems, and Computers (ACSSC 2021), Pacific Grove, CA, USA, 31 Oct.-3 Nov. 2021. p. 1151-1155. DOI : 10.1109/IEEECONF53345.2021.9723288.A 0.4 nJ Excitation Energy Bridge-to-Digital Converter for Implantable Pulmonary Artery Pressure Monitoring

2021-10-07. 2021 IEEE Biomedical Circuits and Systems Conference (BioCAS), Berlin, Germany, October 7-9, 2021. DOI : 10.1109/BioCAS49922.2021.9644941.An Introduction to MPEG-G: The First Open ISO/IEC Standard for the Compression and Exchange of Genomic Sequencing Data

Proceedings Of The Ieee. 2021-09-01. Vol. 109, num. 9, p. 1607-1622. DOI : 10.1109/JPROC.2021.3082027.Networks of Ethereum Non-Fungible Tokens: A graph-based analysis of the ERC-721 ecosystem

2021-01-01. 4th IEEE International Conference on Blockchain (Blockchain), ELECTR NETWORK, Dec 06-08, 2021. p. 188-195. DOI : 10.1109/BLOCKCHAIN53845.2021.00033.Methodologies for Synthesizing and Analyzing Dynamic Dataflow Programs in Heterogeneous Systems for Edge Computing

Ieee Open Journal Of Circuits And Systems. 2021-01-01. Vol. 2, p. 769-781. DOI : 10.1109/OJCAS.2021.3116342.Fully Soft-Switched High Step-Up Nonisolated Three-Port DC-DC Converter Using GaN HEMTs

Ieee Transactions On Industrial Electronics. 2020-10-01. Vol. 67, num. 10, p. 8371-8380. DOI : 10.1109/TIE.2019.2944068.Pipeline Synthesis and Optimization from Branched Feedback Dataflow Programs

Journal Of Signal Processing Systems For Signal Image And Video Technology. 2020-07-11. Vol. 92, p. 1091–1099. DOI : 10.1007/s11265-020-01568-5.High Precision Capacitive Moisture Sensor for Polymers: Modeling and Experiments

IEEE Sensors Journal. 2020-03-15. Vol. 20, num. 6, p. 3032-3039. DOI : 10.1109/JSEN.2019.2957108.CMOS-Based Readout and Control Electronics for Microgrippers

2020-01-01. IEEE Sensors Conference, ELECTR NETWORK, Oct 25-28, 2020. DOI : 10.1109/SENSORS47125.2020.9278921.Programming Heterogeneous CPU-GPU Systems by High-Level Dataflow Synthesis

2020. 2020 IEEE Workshop on Signal Processing Systems (SiPS), [Virtual Conference], October 20 – 22, 2020. p. 1-6. DOI : 10.1109/SiPS50750.2020.9195250.Low-Cost Readout Electronics for Piezoresistive MEMS-Based Transducers

2019-01-01. IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Auckland, NEW ZEALAND, May 20-23, 2019. p. 1597-1601. DOI : 10.1109/I2MTC.2019.8826916.On the relevance of quality score metadata in genomic sequence data for omics applications

Lausanne, EPFL, 2019.A CMOS Analog Front-End for Implantable Pulmonary Artery Pressure Monitoring System

2019-01-01. 15th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), Lausanne, SWITZERLAND, Jul 15-18, 2019. p. 261-264. DOI : 10.1109/PRIME.2019.8787811.An Heterogeneous Compiler Of Dataflow Programs For Zynq Platforms

2019-01-01. 44th IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), Brighton, ENGLAND, May 12-17, 2019. p. 1537-1541. DOI : 10.1109/ICASSP.2019.8682525.Modeling Dielectric Constant Variability in Aggregate Polymers from CV Measurements

2019-01-01. Latin American Electron Devices Conference (LAEDC), Armenia, Colombia, February 24-27, 2019. p. 100-103. DOI : 10.1109/LAED.2019.8714730.Composite Data Types in Dynamic Dataflow Languages as Copyless Memory Sharing Mechanism

2019-06-08. Computational Science – ICCS 2019. p. 717-724. DOI : 10.1007/978-3-030-22750-0_70.Toward a Dynamic Threshold for Quality-Score Distortion in Reference-Based Alignment

2019. 15th International Symposium on Bioinformatics Research and Applications (ISBRA), Barcelona, Spain, June 3–6, 2019. p. 288-300. DOI : 10.1089/cmb.2019.0333.Execution Trace Graph of Dataflow Process Networks

Ieee Transactions On Multi-Scale Computing Systems. 2018-07-01. Vol. 4, num. 3, p. 340-354. DOI : 10.1109/TMSCS.2018.2790921.Shared-variable Synchronization Approaches for Dynamic Data Flow Programs

2018-01-01. IEEE International Workshop on Signal Processing Systems (IEEE SiPS), Cape Town, SOUTH AFRICA, Oct 21-24, 2018. p. 263-268. DOI : 10.1109/SiPS.2018.8598431.Efficient Dynamic Optimisation Heuristics for Dataflow Pipelines

2018-01-01. IEEE International Workshop on Signal Processing Systems (IEEE SiPS), Cape Town, SOUTH AFRICA, Oct 21-24, 2018. p. 337-342. DOI : 10.1109/SiPS.2018.8598386.High Precision Capacitive Moisture Sensor for Polymers

2018-01-01. 17th IEEE SENSORS Conference, New Delhi, INDIA, Oct 28-31, 2018. p. 212-215. DOI : 10.1109/ICSENS.2018.8589775.Lossy compression of quality scores in differential gene expression: A first assessment and impact analysis

2018. Data compression conference (DCC), Snowbird, Utah, March 27-30, 2018. p. 167-176. DOI : 10.1109/DCC.2018.00025.Transcriptome reconstruction with quality score distortion in reference-based alignment

Research in computational molecular biology (RECOMB), Paris, France, April 19-24, 2018.High-Precision Performance Estimation for the Design Space Exploration of Dynamic Dataflow Programs

IEEE Transactions on Multi-Scale Computing Systems. 2018. Vol. 4, num. 2, p. 127-140. DOI : 10.1109/TMSCS.2017.2774294.Design space exploration of dataflow-based Smith-Waterman FPGA implementations

2017-10-03. Signal Processing Systems (SiPS), 2017 IEEE International Workshop on. p. 1-6. DOI : 10.1109/SiPS.2017.8109982.Buffer dimensioning for throughput improvement of dynamic dataflow signal processing applications on multi-core platforms

2017-08-28. p. 1339-1343. DOI : 10.23919/EUSIPCO.2017.8081426.High level synthesis of Smith-Waterman dataflow implementations

2017-03-05. p. 1173-1177. DOI : 10.1109/ICASSP.2017.7952341.Performance estimation of program partitions on multi-core platforms, 2016 26th International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS)

2017-09-21. p. 1-8. DOI : 10.1109/PATMOS.2016.7833418.MPEG-G the emerging standard for genomic data compression

2017. Rocky 2017 Bioinformatics Conference, Aspen, Colorado, USA, December 7-9, 2017.Differential gene expression with lossy compression of quality scores in RNA-seq data

2017. Data Compression Conference (DCC), Snowbird, UT, APR 04-07, 2017. p. 444-444. DOI : 10.1109/Dcc.2017.75.Systematic Design Space Exploration of Dynamic Dataflow Programs for Multi-core Platforms

Lausanne, EPFL, 2017.On the Development and Optimization of HEVC Video Decoders Using High-Level Dataflow Modeling

Journal of Signal Processing Systems. 2016-03-05. Vol. 87, num. 1, p. 127-138. DOI : 10.1007/s11265-016-1113-x.Clock-Gating of Streaming Applications for Energy Efficient Implementations on FPGAs

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 2016-08-02. Vol. 36, num. 4, p. 699-703. DOI : 10.1109/TCAD.2016.2597215.Trace-based manycore partitioning of stream-processing applications

2016-11-06. p. 422-426. DOI : 10.1109/ACSSC.2016.7869073.High-level system synthesis and optimization of dataflow programs for MPSoCs

2016-11-06. p. 417-421. DOI : 10.1109/ACSSC.2016.7869072.High-level synthesis of dynamic dataflow programs on heterogeneous MPSoC platforms

2016-07-17. p. 227-234. DOI : 10.1109/SAMOS.2016.7818352.Design Space Exploration Problem Formulation for Dataflow Programs on Heterogeneous Architectures

2016-09-21. p. 217-224. DOI : 10.1109/MCSoC.2016.25.Programming Models and Methods for Heterogeneous Parallel Embedded Systems

2016-09-21. p. 289-296. DOI : 10.1109/MCSoC.2016.39.High-Precision Performance Estimation of Dynamic Dataflow Programs

2016-09-21. p. 101-108. DOI : 10.1109/MCSoC.2016.23.Comparison of high-throughput sequencing data compression tools

Nature Methods. 2016. Vol. 13, p. 1005-1008. DOI : 10.1038/nmeth.4037.An Evaluation Framework for Lossy Compression of Genome Sequencing Quality Values

2016. IEEE Data Compression Conference 2016, Snowbird, Utah, USA, DOI : 10.1109/Dcc.2016.39.Performance Estimation Based Multicriteria Partitioning Approach for Dynamic Dataflow Programs

Journal of Electrical and Computer Engineering. 2016-01-01. p. 8536432. DOI : 10.1155/2016/8536432.Dataflow Programs Analysis and Optimization Using Model Predictive Control Techniques. Two Examples of Bounded Buffer Scheduling: Deadlock Avoidance and Deadlock Recovery Strategies

Journal of Signal Processing Systems. 2015. p. 1-11. DOI : 10.1007/s11265-015-1083-4.Automated Design Flow for Multi-Functional Dataflow-Based Platforms

Journal of Signal Processing Systems -Signal Image and Video Technology-. 2015. p. 1-23. DOI : 10.1007/s11265-015-1026-0.A Methodology for Profiling and Partitioning Stream Programs on Many-core Architectures

2015. International Conference on Computational Science (ICCS), Reykjavik, Iceland, June 1-3, 2015. p. 2962-2966. DOI : 10.1016/j.procs.2015.05.498.Execution Trace Graph Based Multi-criteria Partitioning of Stream Programs

2015. International Conference on Computational Science (ICCS), Reykjavik, Iceland, June 1-3, 2015. p. 1443-1452. DOI : 10.1016/j.procs.2015.05.334.Synthesis and Optimization of Pipelines for HW Implementations of Dataflow Programs

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 2015. p. 1-1. DOI : 10.1109/TCAD.2015.2427278.Analysis and optimization of dynamic dataflow programs

Lausanne, EPFL, 2015.Actor Merging for Dataflow Process Networks

Ieee Transactions On Signal Processing. 2015. Vol. 63, num. 10, p. 2496-2508. DOI : 10.1109/Tsp.2015.2411229.High-level synthesis of dataflow programs for heterogeneous platforms

Lausanne, EPFL, 2015.MPEG high efficient video coding stream programming and many-cores scalability

2014.TURNUS: An open-source design space exploration framework for dynamic stream programs

2014. 2014 Conference on Design and Architectures for Signal and Image Processing (DASIP), Madrid, Spain, 8-10 October 2014. p. 1-2. DOI : 10.1109/DASIP.2014.7115614.Execution trace graph analysis of dataflow programs: Bounded buffer scheduling and deadlock recovery using model predictive control

2014. 2014 Conference on Design and Architectures for Signal and Image Processing (DASIP), Madrid, Spain, 8-10 October 2014. p. 1-6. DOI : 10.1109/DASIP.2014.7115623.Characterizing communication behavior of dataflow programs using trace analysis

2014. 2014 International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS XIV), Agios Konstantinos, Samos, Greece, 14-17 July 2014. p. 44-50. DOI : 10.1109/SAMOS.2014.6893193.Exploring MPEG HEVC decoder parallelism for the efficient porting onto many-core platforms

2014. 2014 IEEE International Conference on Image Processing (ICIP), Paris, France, 27-30 October 2014. p. 2115-2119. DOI : 10.1109/ICIP.2014.7025424.Dataflow programs analysis and optimization using model predictive control techniques: An example of bounded buffer scheduling

2014. 2014 IEEE Workshop on Signal Processing Systems (SiPS), Belfast, United Kingdom, 20-22 October 2014. p. 1-6. DOI : 10.1109/SiPS.2014.6986054.Automated design flow for coarse-grained reconfigurable platforms: An RVC-CAL multi-standard decoder use-case

2014. 2014 International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS XIV), Agios Konstantinos, Samos, Greece, 14-17 July 2014. p. 59-66. DOI : 10.1109/SAMOS.2014.6893195.Coarse Grain Clock Gating Of Streaming Applications In Programmable Logic Implementations

2014. 4th Electronic System Level Synthesis Conference (ESLsyn), San Francisco, CA, MAY 31-JUN 01, 2014. DOI : 10.1109/ESLsyn.2014.6850387.A Methodology For Optimizing Buffer Sizes Of Dynamic Dataflow Fpgas Implementations

2014. IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), Florence, ITALY, MAY 04-09, 2014. p. 5003-5007. DOI : 10.1109/ICASSP.2014.6854554.ECMA-407: A New 3D audio codec implementation up to NHK 22.2

2014. The 28th VDT International Convention 2014.ECMA-407: New Approaches to 3D Audio Content Data Rate Reduction with RVC-CAL

2014. 137th International Audio Engineering Society (AES) Convention, Los Angeles, California, USA, October 9-12, 2014.Optimizing Dataflow Programs for Hardware Synthesis

Lausanne, EPFL, 2014.High-level dataflow design of signal processing systems for reconfigurable and multicore heterogeneous platforms

Journal Of Real-Time Image Processing. 2014. Vol. 9, num. 1, p. 251-262. DOI : 10.1007/s11554-013-0326-5.Automated Qoe Evaluation Of Dynamic Adaptive Streaming Over Http

2013. 5th International Workshop on Quality of Multimedia Experience (QoMEX). p. 58-63. DOI : 10.1109/QoMEX.2013.6603211.Partitioning And Optimization Of High Level Stream Applications For Multi Clock Domain Architectures

2013. IEEE Workshop on Signal Processing Systems (SiPS). p. 177-182. DOI : 10.1109/SiPS.2013.6674501.Methods to explore design space for MPEG RMC codec specifications

Signal Processing-Image Communication. 2013. Vol. 28, num. 10, p. 1278-1294. DOI : 10.1016/j.image.2013.08.012.Reconfigurable media coding: An overview

Signal Processing-Image Communication. 2013. Vol. 28, num. 10, p. 1215-1223. DOI : 10.1016/j.image.2013.08.008.Modeling Control Tokens for Composition of CAL Actors

2013. Conference on Design and Architectures for Signal and Image Processing (DASIP), Cagliari, Italy, October 8-10, 2013. p. 71-78.Static and quasi-static compositions of stream processing applications from dynamic dataflow programs

2013. IEEE International Conference on Acoustics, Speech and Signal Processing, Vancouver, Canada, May 26-31, 2013. p. 2620-2624. DOI : 10.1109/ICASSP.2013.6638130.Systems Design Space Exploration by Serial Dataflow Program Executions

2013. Asilomar Conference on Signals, Systems, and Computers, Pacific Grove, CA, USA, 3-6 November, 2013. p. 1805-1809. DOI : 10.1109/ACSSC.2013.6810613.Multi-clock domain optimization for reconfigurable architectures in high-level dataflow applications

2013. Asilomar Conference on Signals, Systems, and Computers, Pacific Grove, CA, USA, 3-6 November, 2013. p. 1796-1800. DOI : 10.1109/ACSSC.2013.6810611.Dataflow Program Analysis and Refactoring Techniques for Design Space Exploration: MPEG-4 AVC/H.264 Decoder Implementation Case Study

2013. Design & Architectures for Signal & Image Processing (DASIP), Cagliari, Italy, October 8-10, 2013. p. 63-70.Porting an MPEG-HEVC decoder to a low-power many-core platform

2013. Asilomar Conference on Signals, Systems, and Computers, Pacific Grove, California, USA, November 3-6th, 2013.High-Level Synthesis of Dataflow Programs for Signal Processing Systems

2013. 8th International Symposium on Image and Signal Processing and Analysis (ISPA 2013), Trieste, Italy, 4-6, September 2013. p. 750-754. DOI : 10.1109/ISPA.2013.6703837.Design Space Exploration and Implementation of RVC-CAL Applications using the TURNUS framework

2013. Conference on Design & Architectures for Signal & Image Processing, Cagliari, Italy, 8-10 October 2013. p. 341-342.TURNUS: A design exploration framework for dataflow system design

2013. 2013 IEEE International Symposium on Circuits and Systems (ISCAS), Beijing, China, 19-23 05 2013. p. 654-654. DOI : 10.1109/ISCAS.2013.6571927.Synthesis and optimization of high-level stream programs

2013. Electronic System Level Synthesis Conference (ESLsyn), Austin, Texas, USA, May 31 2013-June 1 2013.Buffer optimization based on critical path analysis of a dataflow program design

2013. 2013 IEEE International Symposium on Circuits and Systems (ISCAS), Beijing, China, 19-23 05 2013. p. 1384-1387. DOI : 10.1109/ISCAS.2013.6572113.Live demonstration: High level software and hardware synthesis of dataflow programs

2013. 2013 IEEE International Symposium on Circuits and Systems (ISCAS), Beijing, China, 19-23 May 2013. DOI : 10.1109/ISCAS.2013.6571930.Secure Computing with the MPEG RVC Framework

Signal Processing-Image Communication. 2013. Vol. 28, num. 10, p. 1315-1334. DOI : 10.1016/j.image.2013.08.015.Performance Benchmarking of RVC based Multimedia Specifications

2013. 20th IEEE International Conference on Image Processing (ICIP), Melbourne, Australia, September 15-18, 2013. p. 4569-4573. DOI : 10.1109/ICIP.2013.6738941.TURNUS: a unified dataflow design space exploration framework for heterogeneous parallel systems

2013. Conference on Design & Architectures for Signal & Image Processing, Cagliari, Italy, 8-10 October 2013. p. 47-54.Design Space Exploration of High Level Stream Programs on Parallel Architectures: A focus on the Buffer Size Minimization and Optimization Problem

2013. 8th International Symposium on Image and Signal Processing and Analysis, Trieste, Italy, 4-6 September 2013.Representing Guard Dependencies in Dataflow Execution Traces

2013. 2013 Fifth International Conference on Computational Intelligence, Communication Systems and Networks (CICSyN), Madrid, Spain, 5-7 06 2013. p. 291-295. DOI : 10.1109/CICSYN.2013.26.Automated QoE Evaluation of Dynamic Adaptive Streaming over HTTP

2013. Fifth International Workshop on Quality of Multimedia Experience (QoMEX), Klagenfurt, Austria, July 3-5, 2013. p. 58-63. DOI : 10.1109/QoMEX.2013.6603211.Scheduling of dynamic dataflow programs based on state space analysis

2012. IEEE International Conference on Acoustics, Speech and Signal Processing, Kyoto, Japan, March 25-30, 2012. p. 1661-1664. DOI : 10.1109/ICASSP.2012.6288215.Profiling of Dataflow Programs Using Post Mortem Causation Traces

2012. 2012 IEEE Workshop on Signal Processing Systems (SiPS), Quebec City, QC, Canada, 17-19 October 2012. p. 220-225. DOI : 10.1109/SiPS.2012.54.Design space exploration strategies for FPGA implementation of signal processing systems using CAL dataflow program

2012. 2012 Conference on Design and Architectures for Signal and Image Processing, Karlsruhe, Germany, 25 October 2012.Hardware and Software Synthesis of Heterogeneous Systems from Dataflow Programs

Journal of Electrical and Computer Engineering, Special issue on “ESL Design Methodology”. 2012. p. 2. DOI : 10.1155/2012/484962.Portable and scalable parallelism for multi-core and reconfigurable hardware using dataflow programs

2011. MCC2011, Fourth Swedish Workshop on Multicore Computing, Linköping, Sweden, November 23-25, 2011.Building Multimedia Security Applications in the MPEG Reconfigurable Video Coding (RVC) Framework

2011. 13th ACM WS on Multimedia and Security, Buffalo, NY, USA, Sept 29-30, 2011. p. 121-130. DOI : 10.1145/2037252.2037275.Hardware/Software Co-Design of Dataflow Programs for Reconfigurable Hardware and Multi-Core Platforms

2011. DASIP 2011, Conference on Design and Architectures for Signal and Image Processing, Tampere, Finland, Nov 2-4, 2011.A Unified Hardware/Software Co-Synthesis Solution for Signal Processing Systems

2011. DASIP 2011, Conference on Design and Architectures for Signal and Image Processin, Tampere, Finland, Nov 2-4, 2011.Optimization of Portable Parallel Signal Processing Applications by Design Space Exploration of Dataflow Programs

2011. SIPS 2011, IEEE WS on Signal processing Systems, Beirut Lebanon, Oct. 4-7, 2011. p. 43-48. DOI : 10.1109/SiPS.2011.6088947.Scheduling of Dynamic Dataflow Programs with Model Checking

2011. SIPS 2011, IEEE WS on Signal processing Systems, Beirut, Lebanon, Oct. 4-7, 2011. p. 37-42. DOI : 10.1109/SiPS.2011.6088946.Methodology for the Hardware/Software Co-Design of Dataflow Programs

2011. SIPS 2011, IEEE WS on Signal processing Systems, Beirut Lebanon, Oct.4-7, 2011. p. 174-179. DOI : 10.1109/SiPS.2011.6088970.MPEG Reconfigurable Video Representation

The MPEG Representation of Digital Media; Springer, 2011.Optimization Methodologies for Complex FPGA-based Signal Processing Systems with CAL

2011. 2011 Conference on Design and Architectures for Signal and Image Processing, Tampere, Finland, November 2-4, 2011.Methodology and Technique to Improve Throughput of FPGA-based CAL Dataflow Programs: Case Study of the RVC MPEG-4 SP Intra Decoder

2011. 2011 IEEE Workshop on Signal Processing Systems, Beirut, Lebanon, October 4-7, 2011. p. 186-191. DOI : 10.1109/SiPS.2011.6088972.Pipeline Synthesis and Optimization of FPGA-based Video Processing Applications with CAL

Eurasip Journal on Image and Video Processing. 2011. Vol. 2011, p. 19. DOI : 10.1186/1687-5281-2011-19.Dataflow Programming for Systems Design Space Exploration for Multicore Platforms

Lausanne, EPFL, 2011.Guest Editorial: Special Issue on Reconfigurable Guest Editorial: Special Issue on Reconfigurable Video Coding

Journal of Signal Processing Systems. 2011. Vol. 63, p. 177–179. DOI : 10.1007/s11265-009-0418-4.Quasi-Static Scheduling of CAL Actor Networks for Reconfigurable Video Coding

Journal of Signal Processing Systems. 2011. Vol. 63, num. 2, p. 191-202. DOI : 10.1007/s11265-009-0389-5.Automatic synthesis of parsers and validation of bitstreams within the MPEG Reconfigurable Video Coding Framework

Journal of Signal Processing Systems. 2011. Vol. 63, p. 215–225. DOI : 10.1007/s11265-009-0395-7.Automatic mutli-connectivity interface generation for system designs based on a dataflow description

2010.Hardware and software synthesis of image filters from CAL dataflow specification

2010.Generation of Hardware/Software Systems Based on CAL Dataflow Description

Algorithm-Architecture Matching for Signal and Image Processing; Dordrecht: Springer, 2010. p. 275-292.Hardware and Software Synthesis of Image Filters From CAL Dataflow Specification

2010. PRIME 2010, Berlin Institute of Technology, Germany, 18–21 July 2010.Automatic mutli-connectivity interface generation for system designs based on a dataflow description

2010. PRIME 2010, Berlin Institute of Technology, Germany, 18–21 July 2010.High level design space exploration of RVC codec specifications for multi-core heterogeneous platforms

2010. Conference on Design and Architectures for Signal and Image Processing, DASIP, Edinburgh, October 26-28, 2010.RVC-CAL dataflow implementations of MPEG AVC/H.264 CABAC decoding

2010. Conference on Design and Architectures for Signal and Image Processing, DASIP 2010, Edinburgh, October 26-28, 2010.RVC: a Multi-Decoder CAL Composer tool

2010. Conference on Design and Architectures for Signal and Image Processing, DASIP, Edinburgh, October 26-28, 2010.Reconfigurable Video Coding — a Stream Programming Approach to the Specification of New Video Coding Standards

2010. MMSYS 2010, Phoenix, AZ, USA, Feb. 22-23, 2010. p. 223–234. DOI : 10.1145/1730836.1730864.The reconfigurable video coding standard

IEEE Signal Processing Magazine. 2010. Vol. 27, num. 3, p. 157-167. DOI : 10.1109/MSP.2010.936032.MPEG Reconfigurable Video Coding

Handbook of Signal Processing Systems; Springer, 2010. p. 43-67.An adaptive system for real-time scalable video streaming with end- to-end qos control

2010. The 11th International Workshop on Image Analysis for Multimedia Interactive Services (WIAMIS), Desenzano del Garda, Italy, Apr 12 – 14, 2010.Reconfigurable Video coding on Multicore An overview of its main objectives

Ieee Signal Processing Magazine. 2009. Vol. 26, p. 113-123. DOI : 10.1109/MSP.2009.934107.A Computationally Efficient Method for Polyphonic Pitch Estimation

EURASIP Journal on Advances in Signal Processing. 2009. Vol. 2009, p. 729494. DOI : 10.1155/2009/729494.Hardware synthesis of complex standard interfaces using CAL dataflow descriptions

2009. DASIP, Sophia Antipolis, September 22-24, 2009.Algorithm/Architecture Co-Exploration of Visual Computing: Overview and Future Perspectives

IEEE Transactions On Circuits And Systems For Video Technology. 2009. Vol. 19, num. 11, p. 1576-1587. DOI : 10.1109/TCSVT.2009.2031376.Special Issue: Algorithm/Architecture Co-Exploration of Visual Computing on Emerging Platforms

IEEE Transactions on Circuits and Systems for Video Technology. 2009. Vol. 19, num. 11, p. 1573-1575. DOI : 10.1109/TCSVT.2009.2034438.Multiprocessor scheduling of dataflow models within the Reconfigurable Video Coding framework

2009. Conference on Design and Architectures for Signal and Image Processing (DASIP), Sophia Antipolis, France, September 22 – 24, 2009.Motion estimation accelerator with user search strategy for the RVC framework

2009. IEEE International Conference on Image Processing, Cairo, Egypt, November 7-10, 2009. p. 761-764. DOI : 10.1109/ICIP.2009.5414256.CAL Dataflow Components For an MPEG RVC AVC Baseline Encoder

Journal Of Signal Processing Systems For Signal Image And Video Technology. 2009. Vol. 63, p. 227-239. DOI : 10.1007/s11265-009-0399-3.An integrated environment for HW/SW co-design based on a CAL specification and HW/SW code generators

2009. ISCAS 2009, Taipei, Taiwan, May, 2009. p. 799-799. DOI : 10.1109/ISCAS.2009.5117876.Reconfigurable Video Coding : Objectives and Technologies

2009. IEEE International Conference on Image Processing, Cairo, Egypt: 2009, Cairo, Egypt, 7-10 November, 2009. p. 749-752. DOI : 10.1109/ICIP.2009.541427.Adaptation based scalable video delivery and management

Lausanne, EPFL, 2009.Translating Dataflow Programs to Efficient Hardware: an MPEG-4 Simple Profile Decoder Case Study

Design, Automation and Test in Europe (DATE08), Munich, Germany,Video Decoder Reconfigurations and AVS Extensions in the New MPEG Reconfigurable Video Coding Framework

2008. IEEE Workshop on Signal Processing Systems, Washington, D.C. Metro Area, U.S.A, October 8-10, 2008. p. 164-169. DOI : 10.1109/SIPS.2008.4671756.Scheduling Of Dataflow Models Within The Reconfigurable Video Coding Framework

2008. IEEE Workshop on Signal Processing Systems. SiPS 2008., Washington, D.C. Metro Area, U.S.A, October 8-10, 2008. p. 182-187. DOI : 10.1109/SIPS.2008.4671759.Validation of Bitstream Syntax and Synthesis of Parsers in the MPEG Reconfigurable Video Coding Framework

2008. IEEE Workshop on Signal Processing Systems, Washington, D.C. Metro Area, U.S.A, October 8-10, 2008. p. 293-298. DOI : 10.1109/SIPS.2008.4671778.OpenDF – A Dataflow Toolset for Reconfigurable Hardware and Multicore Systems

2008. First Swedish Workshop on Multi-Core Computing, MCC, Ronneby, Sweden, November 27-28, 2008.A co-design platform for Algorithm/Architecture design exploration

2008. IEEE International Conference on Multimedia & Expo, Hannover, Germany, June 23-26, 2008. p. 1069-1072. DOI : 10.1109/ICME.2008.4607623.A Multimedia Terminal for Adaptation and End-to-end QoS Control

2008. IEEE International Conference on Multimedia & Expo (ICME 2008), Hannover, Germany, June 23-26, 2008. p. 433-436. DOI : 10.1109/ICME.2008.4607464.How to Make Stream Processing More Mainstream

2008. Workshop on Streaming Systems: From Web and Enterprise to Multicore, in conjunction with the 41st Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), Como, Italy, November 8, 2008.Music Onset Detection Based on Resonator Time Frequency Image

IEEE Transactions On Audio, Speech And Language Processing. 2008. Vol. 16, num. 8, p. 1685-1695. DOI : 10.1109/TASL.2008.2002042.OpenDF – A Dataflow Toolset for Reconfigurable Hardware and Multicore Systems

ACM SIGARCH Computer Architecture News. 2008. Vol. 36, num. 5, p. 29-35. DOI : 10.1145/1556444.1556449.Dataflow/Actor-Oriented language for the design of complex signal processing systems

2008. Conference on Design and Architectures for Signal and Image Processing, DASIP 2008, Bruxelles, Belgium, 24-26 November 2008. p. 168-175.Efficient Data Flow Variable Length Decoding Implementation for the MPEG Reconfigurable Video Coding Framework

2008. IEEE Workshop on Signal Processing Systems, Washington, D.C. Metro Area, U.S.A, October 8-10, 2008. p. 188-193. DOI : 10.1109/SIPS.2008.4671760.Scheduling Of Dataflow Models Within The Reconfigurable Video Coding Framework

2008. Signal Processing Systems, 2008. SiPS 2008. IEEE Workshop on, Washington, D.C. Metro Area, U.S.A, October 8-10, 2008. p. 182-187. DOI : 10.1109/SIPS.2008.4671759.Validation of Bitstream Syntax and Synthesis of Parsers in the MPEG Reconfigurable Video Coding Framework

2008. 2008 IEEE Workshop on Signal Processing Systems, Washington, D.C. Metro Area, U.S.A, October 8-10, 2008. p. 1520-6130. DOI : 10.1109/SIPS.2008.4671778.Dataflow design of a co-processor architecture for image processing

2008. Conference on Design and Architectures for Signal and Image Processing , DASIP 2008, Bruxelles, Belgium, 24-26 November 2008.Smart camera based on embedded HW/SW coprocessor

EURASIP Journal on Embedded Systems. 2008. Vol. 2008, p. 597872. DOI : 10.1155/2008/597872.A Multimedia Terminal for Adaptation and End-to-end QoS Control

2008. Proceedings of the IEEE International Conference on Multimedia & Expo (ICME 2008)., Hannover, Germany, 2008. p. 433-436. DOI : 10.1109/ICME.2008.4607464.A Multimedia Terminal Supporting Adaptation for QoS Control

2008. 9th International Workshop on Image Analysis for Multimedia Interactive Services (WIAMIS 2008), Klagenfurt, Austria, May 7-9, 2008. p. 113-116. DOI : 10.1109/WIAMIS.2008.54.Multimedia Terminal Architecture: An Inter-Operable Approach

2008. The First ACS/IEEE International Workshop on Wireless Internet Services (WISe’08) in conjunction with The Sixth ACS/IEEE International Conference on Computer Systems and Applications (AICCSA-08), Doha, Qatar, April 1-4 2008. p. 981-986. DOI : 10.1109/AICCSA.2008.4493664.[ISO/IEC MPEG contribution] Function Units for Conversion from Syntax to Sequence of Tokens: BTYPE

2008

[ISO/IEC MPEG contribution] Functional Units for RVC Toolbox: Variable Length Decoding

2008

[ISO/IEC MPEG contribution] Auto-generation of RVC Parser from BSDL Syntax Description: Variable Length Decoding

2008

[ISO/IEC MPEG contribution] BSDL Description of MPEG-4 SP and AVC BP Bitstream Syntax for RVC Framework

2008

[ISO/IEC MPEG contribution] Update of Classification of Tokens for FUs of MPEG-4 SP and MPEG-4/AVC in RVC Framework

2008

Smart camera with embedded co-processor: a postal sorting application

2008. Optical and Digital Image Processing, Strasbourg, France, April 7 2008. p. 70000K. DOI : 10.1117/12.781058.A new time-frequency representation for music signal analysis: Resonator Time-Frequency Image

2007. 9th International Symposium on Signal Processing and its Applications, Sharjah, U ARAB EMIRATES, Feb 12-15, 2007. p. 1278-1281. DOI : 10.1109/ISSPA.2007.4555594.A Simplified 8 × 8 Transformation And Quantization Real-Time Ip-Block For MPEG-4 H.264/AVC Applications: A New Design Flow Approach

Journal of Circuits, Systems, and Computers. 2007. Vol. 16, num. 6, p. 1011-1026. DOI : 10.1142/S021812660700399X.Reconfigurable Media Coding: Self-Describing Multimedia Bitstreams

2007. SIPS 2007, Shanghai, Oct. 17-19 2007. p. 319-324. DOI : 10.1109/SIPS.2007.4387565.[ISO/IEC MPEG contribution] Implement flexible FUs according to the processing mechanism in CVC WD using CAL (Results of Core Experiment 1.1) and analysis of the compactness of RVC Abstract Decoder Model (Results of Core Experiment 1.3)

2007

High Performance Embedded Co-Processor Architecture For CMOS Imaging Systems

2007. Workshop on Design and Architectures for Signal and Image Processing, Grenoble (France), November 2007.A HW/SW codesign platform for Algorithm-Architecture mapping

2007. Workshop on Design and Architectures for Signal and Image Processing (DASIP), Grenoble, France, November 27-29.[ISO/IEC MPEG contribution] Classification of Tokens for FUs of MPEG-4 SP and MPEG-4/AVC in RVC Framework

2007

[ISO/IEC MPEG contribution] A systematic procedure for the generation of a CAL parser from BDSL in the RVC framework – result CE 1.1

2007

[ISO/IEC MPEG contribution] Serialized version of some MPEG-4 SP FUs

2007

[ISO/IEC MPEG contribution] Reconfigurability potential of the MPEG-4 SP decoder (results of CE 1.1)

2007

[ISO/IEC MPEG contribution] Implementation of multiple reference frame support in RVC CAL model

2007

[ISO/IEC MPEG contribution] Compression of the RVC DDL Decoder Description with BiM (results of Core Experiment 1.3 in RVC)

2007

[ISO/IEC MPEG contribution] RVC Functional Units naming process proposal

2007

[ISO/IEC MPEG contribution] Update of the Textual specification of Functional Units, DDL and FUs SW of the MPEG-4 SP RVC Abstract Decoder Model (Results of CE 2.1)

2007

[ISO/IEC MPEG contribution] A proposal for the classification and mapping of MPEG video coding technology into Functional Units for the RVC framework (Results of CE 2.2)

2007

A platform for mixed HW/SW algorithm specifications for the exploration of SW and HW partitioning

2007. PATMOS, Göteborg, Sweden, September 3-5, 2007. p. 485-494. DOI : 10.1007/978-3-540-74442-9_47.Reconfigurable media coding: a new specification model for multimedia coders

2007. SiPS, Shanghai, China, October 17-19, 2007. p. 481-486. DOI : 10.1109/SIPS.2007.4387595.Deep-submicron embedded processor architectures for high-performance, low-cost and low-power

Lausanne, EPFL, 2007.A profiling framework for high level design space exploration for memory and system architectures

Lausanne, EPFL, 2007.SMIL to MPEG-4 BIFS Conversion

2006. The Second International Conference on Automated Production of Cross Media Content for Multi-Channel Distribution (AXMEDIS’06), Leeds, UK, December 13-15, 2006. p. 77-84. DOI : 10.1109/AXMEDIS.2006.49.[ISO/IEC MPEG contribution] Report on results of RVC CE 2.1 Reshape the current MPEG-4 SP CAL decoder according to the current FU interface in RVC WM

2006

[ISO/IEC MPEG contribution] Report on results of RVC CE 2.2: Explore the extensibility of FUs

2006

Feature extraction of musical content for automatic music transcription

Lausanne, EPFL, 2006.Configurable motion-estimation hardware accelerator module for the MPEG-4 reference hardware description platform

2005. IEEE International Conference on Image Processing, ICIP 2005, Genova, September 11-14, 2005. p. 591-594. DOI : 10.1109/ICIP.2005.1530573.A Virtual Socket Framework for Rapid Emulation of Video and Multimedia Designs

2005. ICME 2005, Amsterdam, July 6-8, 2005. p. 872-875. DOI : 10.1109/ICME.2005.1521562.A Software/Hardware Platform For Rapid Prototyping of Video and Multimedia Designs

2005. IWSOC 2005, Banff, July 20-24, 2005. p. 30-33. DOI : 10.1109/IWSOC.2005.27.High Level Extraction of SoC Architectural Information from Generic C Algorithmic Descriptions

2005. IWSOC, Banff, July 20-24, 2005. p. 304-307. DOI : 10.1109/IWSOC.2005.71.High-abstraction level complexity analysis and memory architecture simulations of multimedia algorithms

2005. JFAAA’2005, Dijon, January 18-21, 2005. p. 673-684. DOI : 10.1109/TCSVT.2005.846414.Efficient error correction solutions for OFDM-based wireless video

2005. IEEE, PRIME 2005 Conference, Ph.D. Research In Micro-Electronics & Electronics, Lausanne, July 25-28, 2005. p. 205-208. DOI : 10.1109/RME.2005.1543040.An automatic tool for high-level algorithmic complexity evaluation and optimization for system design

2004. Symposium on Design, Test, Integration and Packaging of MWMS/MOEMS, Montreux , SUISSE, May 12, 2004.Data Dependences Critical Path Evaluation at C/C++ System Level

2003. 13th International Workshop, PATMOS 2003, Turin, Italy, September 10-12, 2003. p. 569-579. DOI : 10.1007/978-3-540-39762-5_63.High-Level Algorithmic Complexity Analysis for the Implementation of a Motion-JPEG2000 Encoder

2003. 13th International Workshop, PATMOS 2003, Turin, Italy, September 10-12, 2003. Proceedings. p. 440-450. DOI : 10.1007/978-3-540-39762-5_50.Embedded co-processor architecture for CMOS based image acquisition

2003. International Conference on Image Processing, ICIP 2003, Barcelona, September 14-17, 2005. p. 591-594. DOI : 10.1109/ICIP.2003.1246749.Embedded Co-Processor Architecture for CMOS Based Image Acquisition

2003. p. 591-594. DOI : 10.1109/ICIP.2003.1246749.Improving Dvb-T Forward Error Correction By Concatenated Turbo Code Scheme

2003.High-Level Algorithmic Complexity Analysis for the Implementation of a Motion-JPEG2000 Encoder

2003. p. 440-450. DOI : 10.1007/978-3-540-39762-5_50.Lossy compression of TPC data and trajectory tracking efficiency for the ALICE experiment

Nuclear Instruments & Methods in Physics Research Section a-Accelerators Spectrometers Detectors and Associated Equipment. 2003. Vol. 500, num. -2, p. 412-420. DOI : 10.1016/S0168-9002(03)00343-7.High-level algorithmic complexity evaluation for system design

Journal of Systems Architecture. 2003. Vol. 48, num. 13-15, p. 403-427. DOI : 10.1016/S1383-7621(03)00038-9.Techniques for Optimization of Net Algorithms

2002. International Conference on Parallel Computing in Electrical Engineering, PARALEC’02, Warsaw, September 22-25, 2002. p. 211-216. DOI : 10.1109/PCEE.2002.1115242.An interpreted approach to multimedia streams protection

2002. Eusipco 2002, Toulouse, September 2002. p. 63-66.A Scalable And Programmable Architecture For 2-D DWT Decoding

IEEE Transactions on Circuits and Systems for Video Technology. 2002. Vol. 12, num. 8, p. 671-677. DOI : 10.1109/TCSVT.2002.800863.The MIN PFS problem and piecewise linear model estimation

Discrete Applied Mathematics. 2002. Vol. 118, num. 1-2, p. 115-143. DOI : 10.1016/S0166-218X(01)00260-8.Compression of TPC data in the ALICE experiment

Nuclear Instruments & Methods in Physics Research Section a-Accelerators Spectrometers Detectors and Associated Equipment. 2002. Vol. 487, num. 3, p. 542-556. DOI : 10.1016/S0168-9002(01)02195-7.Fast Line Detection Algorithms Based on Combinatorial Optimization

2001. p. 410-419. DOI : 10.1007/3-540-45129-3_37.A System-on-a-chip for Multimedia Stream Processing and Communication

2000.A System-on-a-chip for MPEG-4 Multimedia Stream Processing and Communication

2000. ISCAS 2000 – IEEE International Symposium on Circuits and Systems, Geneva, Switzerland, May 28-31, 2000. p. 690-693. DOI : 10.1109/ISCAS.2000.856154.Scheduling Strategies for 2D Wavelet Coding Implementations

2000.A System-on-a-chip for Multimedia Stream Processing and Communication

2000. p. 690-693. DOI : 10.1109/ISCAS.2000.856154.A VLSI Architecture for MPEG-4 Stream Processing and Communication

2000.A Hardware Oriented Analysis of Cryptographic Systems for Multimedia Applications

2000.An Efficient Host/Co-Processor Solution For Mpeg-4 Audio Composition

IEEE Transactions on Consumer Electronics. 1999. Vol. 45, num. 4, p. 1290-1300. DOI : 10.1109/30.809221.An efficient Host/Co-Processor Solution for MPEG-4 Audio Composition

1999. p. 26-27. DOI : 10.1109/ICCE.1999.785153.Very high throughput Crypto-System Architectures: The RPK Solution

1999. International Conference on Consumer Electronics, Los Angeles, June 22-24, 1999. p. 96-97. DOI : 10.1109/ICCE.1999.785183.Wavelet Image Compression for mobile/portable Application

1999. International Conference on Consumer Electronics, Los Angeles, June 22-24, 1999. p. 374-375. DOI : 10.1109/ICCE.1999.785419.Cryptosystem architectures for very high throughput multimedia encryption: the RPK solution

1999. International Conference on Consumer Electronics, Paphos, Cyprus, September 5-8, 1999. p. 261-264. DOI : 10.1109/ICECS.1999.812273.An efficient line detection algorithm based on a new combinatorial optimization formulation

1998. ICIP 1998. p. 65-69. DOI : 10.1109/ICIP.1998.727123.Vector Tracing Techniques for Motion Estimation Algorithms in Video Coding

1998. p. 2097-2100.An Efficient Motion Estimation Algorithm Based on Tracing Techniques on Large Search Windows

1998. 1998 International Conference on Image Processing. ICIP98, Chicago, Illinois, p. 609-613. DOI : 10.1109/ICIP.1998.727337.A Parallel Multimedia Processor for Macroblok Based Compression Standars

1997. p. 570-573. DOI : 10.1109/ICIP.1997.638835.Computational Graceful Degradation for Video Sequence Ddecoding

1997. p. 330-333. DOI : 10.1109/ICIP.1997.647773.Motion analysis and estimation

Lausanne, EPFL, 1997.Estimating piecewise linear models using combinatorial optimization techniques

1996. p. 815-818.Image Restoration by 1-D Kalman filtering on oriented image decompositions

1996. p. 2271-2274. DOI : 10.1109/ICASSP.1996.545875.Remote teaching by multimedia communications: the BETEL project

1995