Our group develops advanced methods for ultrafast and portable ultrasound imaging, combining deep learning, inverse problems, and statistical modeling to push the boundaries of image quality, quantitative imaging, and hardware efficiency. We design novel reconstruction frameworks that enhance ultrafast B-mode, Doppler, and quantitative modalities by correcting phase aberrations, estimating local speed-of-sound maps, and exploiting physical models of RF signal formation. Our research introduces data-efficient imaging strategies—including sparse-array acquisition, sparse regularization, and compressive multiplexing—that enable high-quality imaging with drastically reduced data rates, supporting the development of next-generation ultra-portable ultrasound devices. We also develop robust methods for image restoration and reflector localization, contributing tools that are both physically grounded and computationally scalable.

Together, these efforts aim to create more accurate, efficient, and versatile ultrasound imaging systems, capable of integrating ultrafast imaging into increasingly compact and accessible platforms.

EPFL Ultrafast Ultrasound Datasets

Dataset associated with the publication: R. Viñals, J.-P. Thiran — Deep Learning-based Inpainting for Sparse Arrays in Ultrafast Ultrasound Imaging, IEEE Transactions on Computational Imaging, 2025.

Ultrasound Imaging Publications

Explore the scientific contributions of our group in ultrasound imaging

LTS5 research in ultrasound imaging

Regularization methods in ultrasound imaging

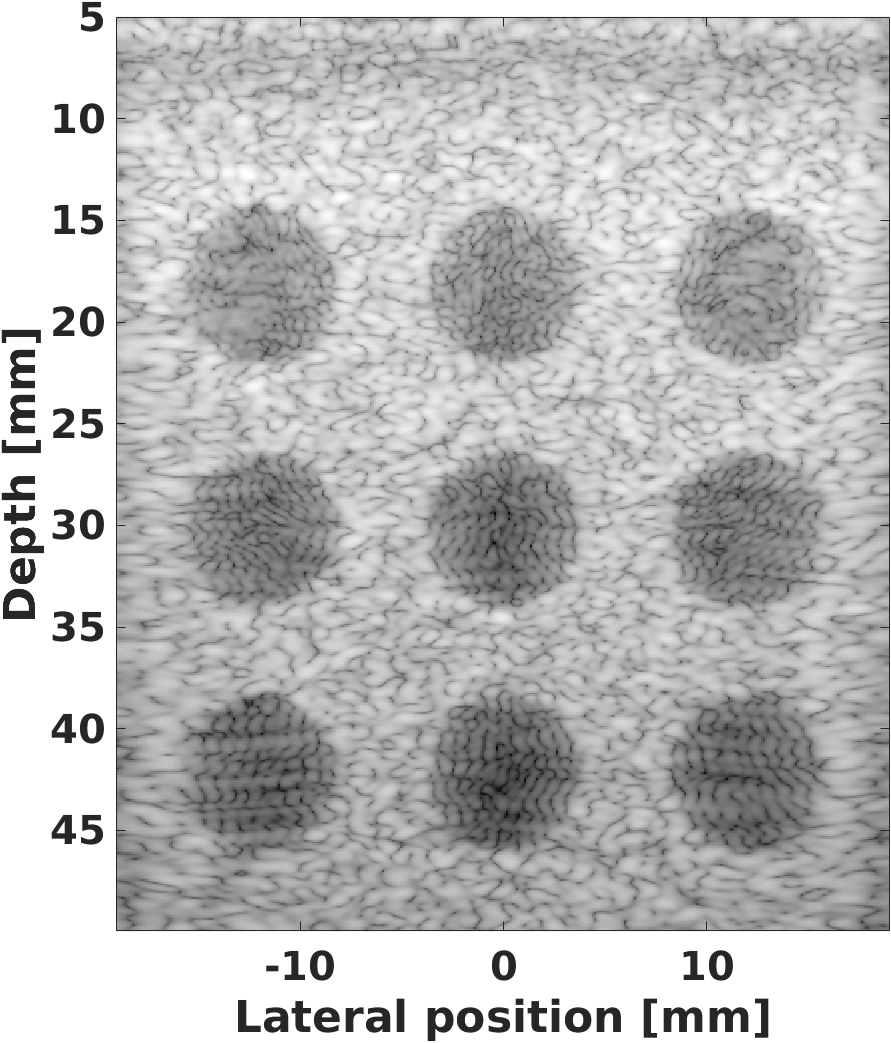

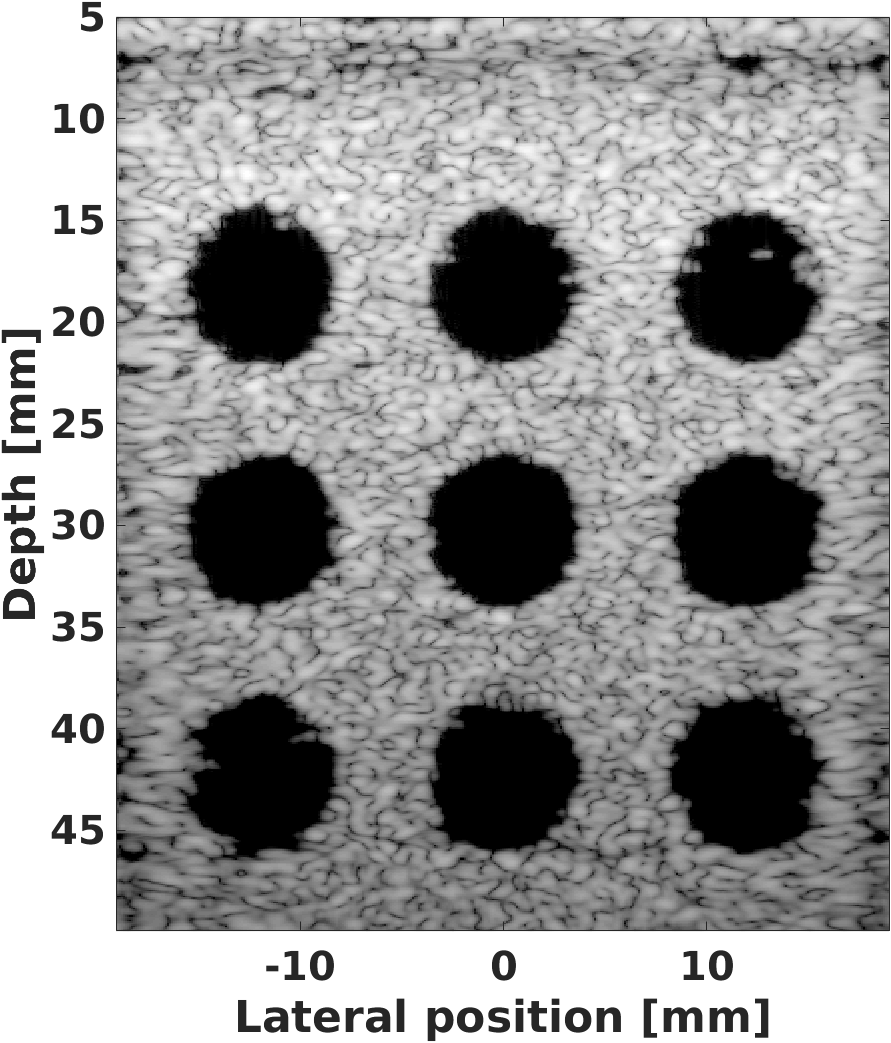

In terms of acoustic wave propagation, ultrasound imaging poses an inverse problem which relates the tissue reflectivity (image under scrutiny) to the backscattered echoes (the measurements). Standard imaging methods are based on a well-known algorithm called Delay-and-sum (DAS). The major advantage of DAS is that it is fast and highly parallelizable. Its main drawback is that it is an inaccurate solution of the inverse problem which leads to low-quality images. One research topic in LTS5 consists in exploring alternatives to DAS mainly based on regularization approaches. The idea is to inject prior knowledge (sparsity of the image in a well-chosen model) about the tissue reflectivity in order to leverage the ill-posedness of the problem. The problem is recast as a convex optimization algorithm and solved using standard algorithms such as ADMM, primal-dual forward backward or FISTA.

Figure: Cyst image reconstructed with the DAS algorithm (left) and with the sparse regularization approach (right).

Compressed sensing and deep learning in ultrasound imaging

Compressed sensing or compressive sensing (CS) is a well-known mathematical framework which ensures perfect recovery of compressible signals from random projections with fewer samples than Nyquist rate. The recovery is achieved by solving a convex optimization problem where the most compressible solution which fits to the measurements is identified. This framework has been substantially studied in the last ten years and has lead to great successes such as: the Rice single pixel camera or the Sparse MRI. At LTS5, we are currently working on applying the CS framework to ultrasound imaging. The first idea is to exploit the intrinsic structure of US data which can be modelled as a stream of pulses, compressible in a redundant dictionary made of shifted replica of the ultrasound pulse. The second idea consists in designing acquisition schemes that are most suited to the CS framework. The last work focuses on designing efficient reconstruction algorithms. To do so, we are intensively working on deep learning algorithms which are becoming extremely popular nowadays due to their ability to perform a various of tasks (object recognition, classification, text generation, image colorization etc.). At LTS5, we are currently focusing on three main deep neural network architectures for ultrasound imaging:

- DNN that maps convex optimization algorithms such as Fast-Iterative thresholding algorithm (FISTA);

- Fully connected architectures (Stacked denoising autoencoders, Multi-layer perceptron);

- Convolutional neural networks.